**GigaDevice Semiconductor Inc.**

# **GD32 MCU GPIO structure and precautions**

# Application Note AN092

Revision 1.3

(July. 2024)

## **Table of Contents**

| Table of | of Contents                                   | .2  |

|----------|-----------------------------------------------|-----|

| List of  | Figures                                       | . 3 |

| List of  | Tables                                        | .4  |

| 1. li    | ntroduction                                   | . 5 |

| 2. 0     | GPIO structure                                | .6  |

| 3. Т     | Typical application scenarios and precautions | . 8 |

| 3.1.     | IO input                                      | . 8 |

| 3.2.     | IO output                                     | . 9 |

| 3.3.     | Other considerations                          | 11  |

| 4. F     | Revision history1                             | 13  |

|          |                                               |     |

# List of Figures

| Figure 2-1. Standard IO basic structure diagram        | . 6 |

|--------------------------------------------------------|-----|

| Figure 2-2. Basic structure diagram of non-5VT IO pins | . 7 |

| Figure 2-3. Basic structure diagram of 5VT IO pin      | . 7 |

| Figure 3-1. Simplified diagram of I/O input circuit    | 12  |

## **List of Tables**

| Table 3-1. Absolute maximum ratings           | 8  |

|-----------------------------------------------|----|

| Table 3-2. GD32F425xx GPIO DC characteristics | 10 |

| Table 4-1. Revision history                   | 13 |

#### 1. Introduction

This article is specially provided for engineers who develop GPIO based on GD32 MCU. It mainly introduces the functional configuration, internal structure and the matters for attention when using GPIO in different scenarios. The purpose of this application notes is to help GD32 MCU users optimize the use of general-purpose input / output ports (GPIO), and correctly and quickly use GD32 MCU for product development.

GPIO, short for general-purpose input / output ports, can be configured with its output or input by software. The GPIO pin of GD32 can be connected with external devices to realize the functions of external communication, control and signal input. It is a common and most widely used module in GD32 MCU.

Each GPIO pin can be configured by software for output (push-pull or open drain), input, peripheral standby, or analog mode. Each GPIO pin can be configured in pull-up, pull-down or non pull-up/non pull-down mode.

GD32 MCU GPIO features:

- Input / output direction control.

- Schmidt trigger input function

- Each pin has a weak pull-up/pull-down function.

- Push-pull/open drain output enable control.

- Set/reset output enable.

- External interrupts for programmable trigger edges use EXTI to configure registers.

- Analog input/output configuration.

- Standby function input/output configuration.

- Port lock configuration.

For GD32, GPIO of some series MCU may have more functions, such as clock, I2C, SPI, CAN, USART, USB, ADC, DAC, etc. Before designing the circuit board, check th e data manual and user manual of the series to compare whether the GPIO used m eets the requirements.

#### 2. GPIO structure

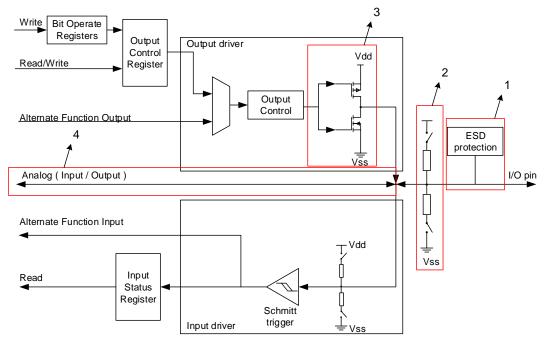

In GD32 MCU, there are usually two types of GPIO, non-5V tolerant IO and 5V tolerant IO(Some MCUs do not have 5VT pins, such as GD32A503xx series). The two types of GPIO are slightly different in structure. *Figure 2-1. Standard IO basic structure diagram*.

Figure 2-1. Standard IO basic structure diagram

I/O pin represents the I/O pad of the chip, which is connected to the external circuit, and other parts of the circuit are the internal circuit of the chip.

The upper part of the block diagram represents the output part of the IO circuit. When the IO uses its standby function to connect other internal peripherals, the relevant power output part of the circuit will also be shared. The bottom half of the block diagram shows the input circuit of the IO, which is also shared with other internal peripherals, such as the Schmidt flip-flop, as a backup function. The middle part of the block diagram, such as the circuit in red box 4, represents the analog input-output channel. The output of the analog channel (such as the DAC output) does not pass through the power output circuit, and the input does not pass through the Schmidt input circuit. The external circuit is directly connected to the internal analog peripheral through the IO pin.

Red box 3 represents the main power circuit of I/O output. Relevant control registers can be configured to control the conduction of the upper and lower MOS tubes to realize push-pull output or open-drain output.

Red box 2 represents the internal pull-up or pull-down circuit of the IO port. The internal pullup or pull-down circuit of the input port can be realized through the configuration of relevant registers. The resistance value of the pull-up/pull-down resistor can be referred to the data manual, and the typical value is  $40k\Omega$ . If the PA10 pin pull-down resistance of GD32F425xx

is 10 k $\Omega$ , see the section GPIO characteristic in the data book for detailed data.

Red box 2 represents ESD protection circuit.

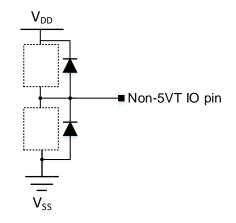

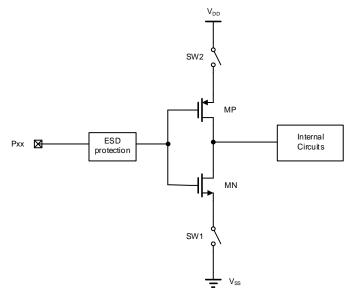

The ESD protection circuit of non-5VT IO is shown in <u>Figure 2-2. Basic structure diagram</u> <u>of non-5VT IO pins</u> shows that the ESD protection circuit forms two diodes respectively in  $V_{DD}$  and  $V_{SS}$  of IO. Obviously, if the voltage ratio of IO to  $V_{DD}$  is greater than the positive guide voltage drop of diode, or the voltage on IO is lower than the potential of  $V_{SS}$ , And the voltage difference is greater than the diode positive guide voltage, will generate a current from IO to  $V_{DD}$ , or from  $V_{SS}$  to IO.

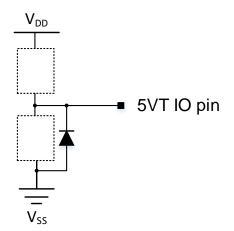

The ESD protection circuit of 5VT IO is shown in *Figure 2-3. Basic structure diagram of* <u>5VT IO pin</u>. The 5VT IO pin is not connected to the internal protection diode of the power supply (V<sub>DD</sub>).

Therefore, in actual use, if the pin is powered on first and the MCU is powered on later, the pin of 5VT is preferred to be used as the pin of external connection to power on first, to avoid the IO pin pulling down due to pin leakage. If standard IO pins must be selected, isolation measures such as triode should be used to prevent pin leakage.

#### Figure 2-2. Basic structure diagram of non-5VT IO pins

Figure 2-3. Basic structure diagram of 5VT IO pin

Note: The internal structure of 5VT IO is partially different from that of non-5VT IO.

## 3. Typical application scenarios and precautions

There are some precautions for using different types of IO. The following describes the typical application scenarios, features and precautions of different types of IO from the perspectives of input and output.

#### 3.1. IO input

The first is the input voltage range of the IO port. The input voltage tolerance value represents the input voltage range that can be tolerated by the IO port, some GD32 MCU contain 5VT IO and non-5VT IO, as shown in *Table 3-1. Absolute maximum ratings* in the data manual, 5VT IO has different characteristics than non-5VT IO.

| Table 3-1 | . Absolute | maximum | ratings |

|-----------|------------|---------|---------|

|-----------|------------|---------|---------|

| Symbol Parameter |                                                 | Min                   | Max                   | Unit |

|------------------|-------------------------------------------------|-----------------------|-----------------------|------|

| Vin              | Input voltage on 5V tolerant pin <sup>(1)</sup> | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 3.6 | V    |

|                  | Input voltage on other I/O                      | V <sub>SS</sub> - 0.3 | 3.6                   | V    |

|                  |                                                 |                       |                       |      |

(1)  $V_{IN}$  maximum value cannot exceed 5.5 V.

For the IO port input scenario, note the following:

- 1. For 5VT IO, when  $V_{DD} = 0$  (when the MCU is not powered on), the pin input voltage cannot exceed 3.6V.

- We need to carefully choose 5VT IO or non-5VT IO according to the voltage range of the external input signal of the IO port. If the input signal is greater than 5.5V, the signal should be adjusted into a suitable range and then sent to the IO port of the MCU.

- 3. The low level of GPIO input is  $\leq 0.3 V_{DD}$ , and the high level of GPIO input is  $\geq 0.7 V_{DD}$ .

- 4. According to the typical structure of IO ports of different types described above, if the voltage on non-5VT IO is more than 0.3V larger than the voltage of V<sub>DD</sub>, it may cause leakage of IO in ESD protection circuit to the diode conduction of V<sub>DD</sub>, especially in the case that the MCU is not powered on and the IO port has already been charged. If 5VT IO is selected, the leakage from IO to V<sub>DD</sub> will be avoided. Typically, if the IO is connected to the I2C bus, we need to select the 5VT pin.

- 5. When all I/Os of the MCU are powered on and no other configuration is performed, they work in the floating input mode by default, and the debug port is pull-up or pull-down mode. For details about pull-up or pull-down, see the user manual. Therefore, in some scenarios where a fixed level needs to be generated, if the MCU is reset from standby mode, the default input pull-down state of these I/O ports needs to be considered, and the default state will not change until the program reconfigures the state of these I/Os.

- 6. In order to achieve lower power consumption, especially in sleep mode and deep sleep mode, the unused IO needs to be configured as analog input, or configured as floating input state with external drop-down, or set as internal drop-down or drop-down. Note that when internal pull-down is used, external hardware pull-down is not required to avoid extra power consumption. External hardware cannot be pulled up (the IO not used here

also includes the IO not elicited on this wrapper). For GD32 low-power MCU products, the best power performance will also be achieved in run mode with Settings as described previously.

- 5VT IO can input up to 5.5V only in input mode. When output mode is enabled, 5VT IO can no longer withstand 5.5V voltage. For details on the I/O input voltage, refer to the V<sub>IN</sub> parameter in the Datasheet Common Operating Conditions Table.

- Only when the analog function is not enabled on the pin, 5VT IO can input the maximum voltage of 5.5V. If some analog input functions (ADC input active, COMP input, OPAMP input) are enabled on the 5VT IO, then the maximum operating voltage on the pin cannot exceed min(V<sub>DDA</sub>, V<sub>REFP</sub>) + 0.3V.

#### 3.2. IO output

There are also some important points to note in the IO output scenario:

- 1. There is a very significant relationship between the open-drain output voltage and the output on-load current. Generally, when the output of IO is high, the higher the load is, the lower the output high level will be. Similarly, when the output of IO is low, the greater the current flowing into IO is, the higher the output low level will be.

- 2. For the model with backup domain in MCU, some IO works in the power supply of the backup domain, and the carrying capacity of these IO is limited. It is recommended to set the IO speed parameter of these IO to the lowest speed (generally 2MHz). For example, the four pins PC13, PC14, PC15 and PI8 in GD32F4xx series are different for different series with weak driving ability. Detailed information can be queried in the data manual of this series.

- 3. The passable current of GPIO is related to the IO configuration speed. At present, the maximum passable current of IO of all GD32 MCU is 25 mA (excluding pins working in the backup domain), and the source current and sink current of GPIO shall not exceed 25 mA. When GPIO speed configuration is low, its source current and sink current capacity may not reach 25 mA.

- 4. Some GD32 MCU contain I/O compensation units, such as E50x series. By default, the I/O compensation unit is not used. When the output speed of the I/O port is greater than 50MHz, you are advised to use the I/O compensation unit to control the slope of the I/O port to reduce the impact of I/O port noise on the working power supply.

- 5. The overshoot of IO will increase with the increase of the speed of IO port during the high and low level conversion. The overshoot can be reduced by reducing the speed of IO port.

- The high and low level of GPIO output is not absolute zero or V<sub>DD</sub>, but varies with the speed of IO configuration, V<sub>DD</sub> voltage and output current. As shown in <u>Table 3-2</u>. <u>GD32F425xx GPIO DC characteristics</u>, the data table of GD32F425xx GPIO output high and low levels varies with these variables.

# AN092 GD32 MCU GPIO structure and precautions

#### Table 3-2. GD32F425xx GPIO DC characteristics

| Symbol          | Parameter                  | Conditions              | Min  | Тур | Max  | Unit |

|-----------------|----------------------------|-------------------------|------|-----|------|------|

|                 |                            | IO_Speed:level 3        |      |     |      | 1    |

|                 | Low level output           | V <sub>DD</sub> = 2.6 V |      | _   | 0.11 |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V |      |     | 0.10 |      |

|                 | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V |      | _   | 0.10 |      |

| Vol             | Low level output           | V <sub>DD</sub> = 2.6 V |      | —   | 0.29 |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | _    | —   | 0.27 |      |

|                 | (I <sub>IO</sub> = +20 mA) | V <sub>DD</sub> = 3.6 V | _    | —   | 0.26 | .,   |

|                 | High level output          | V <sub>DD</sub> = 2.6 V | 2.46 | —   |      | V    |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 3.18 | —   |      |      |

| N/              | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V | 3.48 | —   |      |      |

| V <sub>OH</sub> | High level output          | V <sub>DD</sub> = 2.6 V | 2.22 | —   |      |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 2.98 |     |      |      |

|                 | (I <sub>IO</sub> = +20 mA) | V <sub>DD</sub> = 3.6 V | 3.29 | —   |      |      |

|                 |                            | IO_Speed:level 2        |      |     |      | •    |

|                 | Low level output           | V <sub>DD</sub> = 2.6 V | _    |     | 0.16 |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | _    | _   | 0.14 | 1    |

| V               | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V | —    |     | 0.14 |      |

| V <sub>OL</sub> | Low level output           | V <sub>DD</sub> = 2.6 V | —    |     | 0.43 | 1    |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | _    | —   | 0.37 |      |

|                 | (I <sub>IO</sub> = +20 mA) | V <sub>DD</sub> = 3.6 V | —    | —   | 0.36 | v    |

|                 | High level output          | V <sub>DD</sub> = 2.6 V | 2.40 | —   | _    | v    |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 3.12 | —   |      |      |

| Mari            | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V | 3.44 | —   |      |      |

| Vон             | High level output          | V <sub>DD</sub> = 2.6 V | 2.05 | —   | _    |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 2.84 | —   | _    |      |

|                 | (I <sub>IO</sub> = +20 mA) | V <sub>DD</sub> = 3.6 V | 3.17 | —   | _    |      |

|                 |                            | IO_Speed:level 1        |      |     |      |      |

|                 | Low level output           | V <sub>DD</sub> = 2.6 V | _    | —   | 0.28 |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | _    | —   | 0.28 |      |

|                 | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V | —    | —   | 0.24 |      |

| Vol             | (I <sub>IO</sub> = +15 mA) | V <sub>DD</sub> = 2.6 V | —    | —   | 0.57 |      |

|                 | Low level output           | V <sub>DD</sub> = 3.3 V | _    | _   | 0.66 |      |

|                 | voltage for an IO Pin      |                         |      |     |      | -    |

|                 | (I <sub>IO</sub> = +20 mA) | V <sub>DD</sub> = 3.6 V | —    |     | 0.64 | V    |

|                 | High level output          | V <sub>DD</sub> = 2.6 V | 2.23 | —   | _    |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 3.00 | —   | _    |      |

|                 | (I <sub>IO</sub> = +8 mA)  | V <sub>DD</sub> = 3.6 V | 3.31 | —   |      |      |

| Vон             | (I <sub>IO</sub> = +15 mA) | V <sub>DD</sub> = 2.6 V | 1.83 | _   |      |      |

|                 | High level output          | V <sub>DD</sub> = 3.3 V | 2.45 | _   | _    |      |

|                 | voltage for an IO Pin      | V <sub>DD</sub> = 3.6 V | 2.81 | 1   |      | 1    |

## AN092 GD32 MCU GPIO structure and precautions

| Symbol | Parameter                  | Conditions              | Min  | Тур | Max  | Unit |

|--------|----------------------------|-------------------------|------|-----|------|------|

|        | (I <sub>IO</sub> = +20 mA) |                         |      |     |      |      |

|        |                            | IO_Speed:level 0        |      |     |      |      |

|        | Low level output           | V <sub>DD</sub> = 2.6 V | —    | —   | 0.17 |      |

|        | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | _    | —   | 0.15 |      |

| Vol    | (I <sub>IO</sub> = +1 mA)  | V <sub>DD</sub> = 3.6 V | _    | _   | 0.15 |      |

| VOL    | Low level output           | V <sub>DD</sub> = 2.6 V | _    | _   | 0.80 |      |

|        | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | —    | —   | 0.63 |      |

|        | (I <sub>IO</sub> = +4 mA)  | V <sub>DD</sub> = 3.6 V | _    | —   | 0.60 | v    |

|        | High level output          | V <sub>DD</sub> = 2.6 V | 2.38 | —   | _    | v    |

|        | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 3.12 | —   | _    |      |

| Vон    | (I <sub>IO</sub> = +1 mA)  | V <sub>DD</sub> = 3.6 V | 3.42 | —   | _    |      |

|        | High level output          | V <sub>DD</sub> = 2.6 V | 1.45 | —   | _    |      |

|        | voltage for an IO Pin      | V <sub>DD</sub> = 3.3 V | 2.48 | —   | _    |      |

|        | (I <sub>IO</sub> = +4 mA)  | V <sub>DD</sub> = 3.6 V | 2.83 | —   |      |      |

## 3.3. Other considerations

To better improve the performance of GD32 MCU in some typical application scenarios, note the following when using GPIO of GD32 MCU:

- The ADC input pins of some series GD32 MCU are standard IO pins. Attention should be paid to avoid the ADC input voltage exceeding VDD+0.3V, otherwise the ADC sampling may be abnormal due to leakage; When using the ADC module, all ADC pins shall not introduce negative voltage, otherwise the ADC sampling will be inaccurate.

- 2. The V<sub>BAT</sub> pin allows the GD32 backup domain to be powered from an external voltage source (battery or capacitor). When the GD32 microcontroller is powered only by the V<sub>BAT</sub> pin, only GPIO in the backup domain will work. The GPIO driver of the backup domain is weak and varies according to the backup domain. For applications without external batteries, it is recommended to connect the V<sub>BAT</sub> pin to the V<sub>DD</sub> pin after grounding through the 100nF's external ceramic decoupling capacitor.

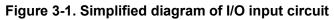

- 3. To improve EMC performance and to avoid the risk of leakage current from floating input I/O pins, it is recommended to use hardware pull-up or pull-down for unused I/O pins. The input circuit of the I/O can be simplified as shown in *Figure 3-1. Simplified diagram* of I/O input circuit, where Pxx represents a specific pin of the MCU. When the I/O is configured in floating input mode, switches SW1 and SW2 are closed. If Pxx is not driven by an external voltage, the voltage of Pxx can be any value between V<sub>SS</sub> and V<sub>DD</sub>. Assuming in *Figure 3-1. Simplified diagram of I/O input circuit* that the threshold voltage of MN is V<sub>THN</sub> and the threshold voltage of MP is V<sub>THP</sub>, when the voltage of Pxx is between V<sub>THN</sub> and (V<sub>DD</sub> V<sub>THP</sub>), both MN and MP are turned on simultaneously, which may result in a significant leakage current between V<sub>DD</sub> and V<sub>SS</sub>.

When the I/O is configured in pull-up mode, pull-down mode, or analog mode, MP and MN will not conduct at the same time, preventing any leakage current between  $V_{DD}$  and

Vss.

4. In multiple groups, only one I/O port of the same label PIN can be configured as external interrupt. For example, only one of the three I/O ports in PA0, PB0, and PC0 can be configured as external interrupt.

## 4. Revision history

#### Table 4-1. Revision history

| Revison No. | Description                                                            | Date          |

|-------------|------------------------------------------------------------------------|---------------|

| 1.0         | Initial Release                                                        | Dec.16, 2022  |

| 1.1         | Updated charts and descriptions                                        | Mar.29, 2023  |

| 1.2         | Remove Figure 2-1 Analog channel<br>switch                             | Jun.21, 2023  |

| 1.3         | Add I/O floating input leakage risk warning and principle introduction | July.15, 2024 |

#### **Important Notice**

This document is the property of GigaDevice Semiconductor Inc. and its subsidiaries (the "Company"). This document, including any product of the Company described in this document (the "Product"), is owned by the Company under the intellectual property laws and treaties of the People's Republic of China and other jurisdictions worldwide. The Company reserves all rights under such laws and treaties and does not grant any license under its patents, copyrights, trademarks, or other intellectual property rights. The names and brands of third party referred thereto (if any) are the property of their respective owner and referred to for identification purposes only.

The Company makes no warranty of any kind, express or implied, with regard to this document or any Product, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. The Company does not assume any liability arising out of the application or use of any Product described in this document. Any information provided in this document is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Except for customized products which has been expressly identified in the applicable agreement, the Products are designed, developed, and/or manufactured for ordinary business, industrial, personal, and/or household applications only. The Products are not designed, intended, or authorized for use as components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, atomic energy control instruments, combustion control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or Product could cause personal injury, death, property or environmental damage ("Unintended Uses"). Customers shall take any and all actions to ensure using and selling the Products in accordance with the applicable laws and regulations. The Company is not liable, in whole or in part, and customers shall and hereby do release the Company as well as it's suppliers and/or distributors from any claim, damage, or other liability arising from or related to all Unintended Uses of the Products. Customers shall indemnify and hold the Company as well as it's suppliers and/or distributors harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of the Products.

Information in this document is provided solely in connection with the Products. The Company reserves the right to make changes, corrections, modifications or improvements to this document and Products and services described herein at any time, without notice.

© 2023 GigaDevice - All rights reserved